# **Hind Photostat & Book Store**

Best Quality Classroom Topper Hand Written Notes to Crack GATE, IES, PSU's & Other Government Competitive/ Entrance Exams

## MADE EASY ELECTRONICS ENGINEERING ADVANCE ELECTRONICS By-KAMESH Sir

- Theory

- Explanation

- Derivation

- Example

- Shortcuts

- Previous Years Question With Solution

visit us:-www.hindphotostat.com

Courier Facility All Over India (DTDC & INDIA POST) Mob-9311989030

#### MADE EASY, IES MASTER, ACE ACADEMY, KREATRYX

#### ESE, GATE, PSU BEST QUALITY TOPPER HAND WRITTEN NOTES MINIMUM PRICE AVAILABLE @ OUR WEBSITE

1. ELECTRONICS ENGINEERING 3.MECHANICAL ENGINEERING 5.INSTRUMENTION ENGINEERING **2. ELECTRICAL ENGINEERING**

- 4. CIVIL ENGINEERING

- 6. COMPUTER SCIENCE

#### **IES , GATE , PSU TEST SERIES AVAILABLE @ OUR WEBSITE**

IES – PRELIMS & MAINS

✤ GATE

**NOTE;- ALL ENGINEERING BRANCHS**

> ALL <u>PSUS</u> PREVIOUS YEAR QUESTION PAPER @ OUR WEBSITE

### **PUBLICATIONS BOOKS -**

MADE EASY, IES MASTER, ACE ACADEMY, KREATRYX, GATE ACADEMY, ARIHANT, GK

RAKESH YADAV, KD CAMPUS , FOUNDATION , MC – GRAW HILL (TMH) , PEARSON...OTHERS

HEAVY DISCOUNTS BOOKS AVAILABLE @ OUR WEBSITE

F230, Lado Sarai New Delhi-110030 Phone: 9311 989 030 Shop No: 46 100 Futa M.G. Rd Near Made Easy Ghitorni, New Delhi-30 Phone:9711475393 F518 Near Kali Maa Mandir Lado Sarai New Delhi-110030 Phone: 9560 163 471 Shop No.7/8 Saidulajab Market Neb Sarai More, Saket, New Delhi-30

Website: <u>www.hindPhotostat.com</u> Contact Us: 9311 989 030 Courier Facility All Over India (DTDC & INDIA POST)

Advanced Electronics

1. VLSI Fabrication 2. VLSI Testing 3. VLSI Design

(7)

٢

9

6)

୍ତି

٩

(ي)

. ()

· (-)

$(\overline{\cdot})$

() }

٩

(i)

$\bigcirc$

()

$\cdot$

$\bigcirc$

$\bigcirc$

٢

()

<u>(</u>)

(j)

(j)

ා ඉ ා

() )

لا بر در لورید رجهاندر BOOKS: 1, S.K Gandhi. 2, S.M SZE.

Important source : Class Notes

્રિ

ੁ

**B** # Integrated Circuits: Ì Circuits: Combination (connection) of Active and . R () passive elements.  $\bigcirc$ Active elements: BJT, MOSFET, JFET. ٩ (j) Passive elements : R.L.C (j) (j) ٢ Integrated Circuit: Active and Passive elements are  $\langle \hat{} \rangle$ fabricated on a <u>Substrate</u>. -> Semiconductor.  $\langle \hat{} \rangle$  $\langle \cdot \rangle$ > Insulator substrate. ( )()Discrete Circuits IC ( )(1. Lauge size. 1. small Size (2. High power consumption. ٢ 2. Low power consumption. 3. High Case. 3. Low cost ( due to Batch Process) Ś .;;) 4. Low speed. 4. High speed. - \_\_\_) eg: PCB (Printed ckt board) Disodvantages of IC: ٢ () \* Non Repairable only we can Replace IC. 83 (1

5,50

Classification of IC's 9 0 ٢ Level of Integration Analog Icig > Monolithic IC4 1 SSI 1. > Thin / Thick film IC's ٢ Digital MSI 2. 0 > Hybrid IC's LSI 3. ٩ Bipolay IC+ VESI ч. ð CMOS IC 5. ULSI Ô BICMOS IC ٩ 0 # Monolithic IC's: 0 ා Mano -> single ా lithic -> stone.  $\bigcirc$ In Mandithic IC's, complete cut (active + pareive element) are fabricated on a single substrate.  $\overline{\mathbf{O}}$  $\bigcirc$  $\bigcirc$  $\bigcirc$ RL MOS ٢ Semiconductor 0 0 Disadvantage: Heavy value of R.L.C cannot be 0 -fabricated. Boz heavy values of R,L,C ٢ ٩ required Lange anea of substrate. ු 0 # Thin & Thick film IC's : ŚŻ Thing Thick film IC's looks very spuilar in ٢ appearance. Only difference is the method by which Ĵ Substrate. the conducting film is deposited on Insulator

> In this technology, the Active element are fabricated on Serviconductor substrate, wheatable Paisive elements are fabricated on Insulator 9 ()substrate. ()#> Heavy value of R.L., C are not restricted in this, ()compared to Manolithic IC's. <u>(</u>) ٢  $\bigcirc$ BJT MOS **Q**  $\left( \cdot \right)$ Insulator sub SC. sub Ì  $\left(\frac{1}{2}\right)$ Thin film Technology Thich film Technology. ٢ -> Conductive film is deposited → Conductive film is  $\left( \cdot \right)$ by screen printing or deposited by sputtering  $(\cdot,\cdot)$ Silly screen printing. technique or by Vapour 신 ) evapowiation. Ð Ì Ð # Hybrid IC's: 299 299 BJT, MOS Monolituic\_ RLC IC' Insulator sub. 83 ٢ # Avalog IC's: (Linear IC's) () En: IC-555, Op-amp 741. 3 I/P: Analog signal ã j O/P: Availing signal ्स्रत्ये

1 # Digital IC's: (Non-Linear IC's) 0  $\bigcirc$ Ex: Flip-Flop 0 I/P > Digital signal ্ট 0/P > Digital signal ා ٩ ٢ # Level of Integration > ٩ ි 1. Small Scale Integration (SSI): 1-10 Tx per unit ୍ (MSI): 10-100 ٩ 2. Medium ٩  $(LSI): 100 - 10^{4}$ Lauge 3.  $\bigcirc$ Vouy Lauge scale Integration (VLSI): 104-1M ਼ 4.  $\bigcirc$ Ultra Large scale Integration (ULSI) 5. ()> 1M Tx per wit of ٢ -the substrate. 0 ( ) · Packing density, P = log, Q. ٢ ٩ Q: NO. Of Tx per unit area. 0 ٢  $\bigcirc$  $SSI \rightarrow (P < 1)$ ()(3) MSI → (1<P<2) ٩ 3 LSI  $\Rightarrow (2 \times P \times 4)$ ා ો  $( \Psi \lor \mathsf{VLSI} \Rightarrow ( \Psi \lor \mathsf{P} \lt \mathsf{G} )$ ٢ S ULSI  $\Rightarrow$  (P>6) ٢

( ) (

0

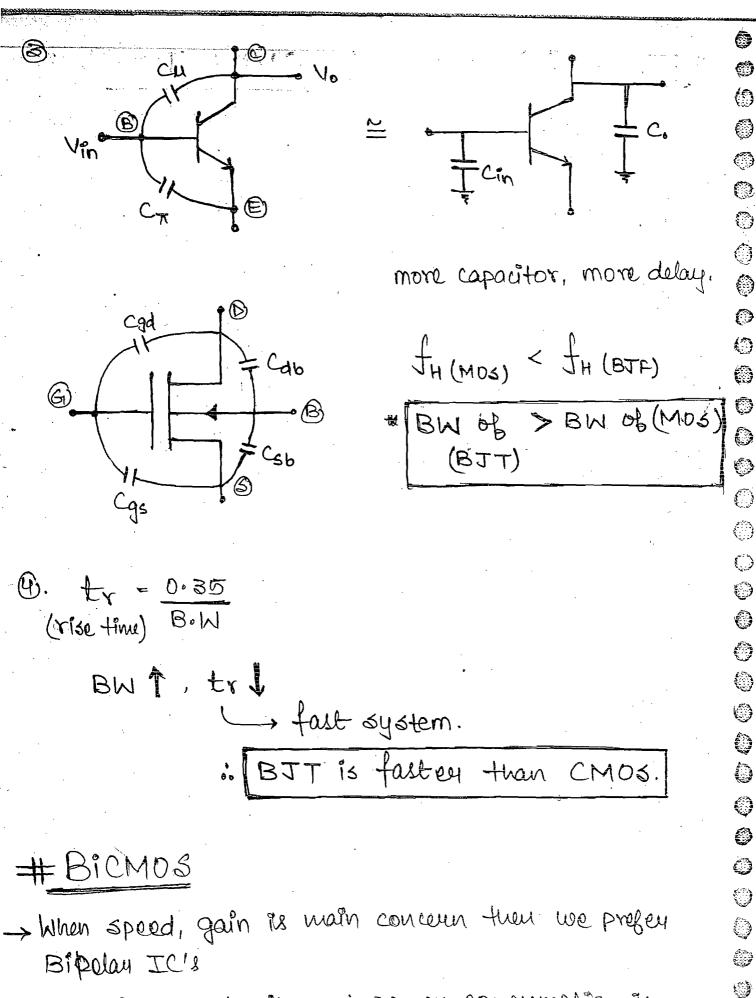

69 CMOS IC'S (NMOS PMOS) # Bipolay IC 's (BJT) Ð O Low packing density ( High Packing deveity () 2 High gain ② Low gain. ( <sup>-</sup>) @ Low Bandwidth. 3 High Bandwidth. <u>(</u>) 6 (9) High Speed. 9 Low speed. (5) High power consumption. ્રિ 5 Low Power Consumption  $( \cdot )$ → Gain = gm (Load) (€}, gm→ Transconductance  $( \ )$  $\langle \rangle$  $\Im m = \frac{I_c}{\eta V_T} = \frac{I_s e^{V_{BE}}/\eta V_T}{\eta V_T}$  $(\cdot)$ ( ) $(\mathbb{R})$ VBET, Ict exponentially, gm Texponentialy. ٩ MOSFET:  $\exists m = \exists D HnCox(\frac{W}{L})$ **.** }  $I_D \ll (V_{GS} - V_T)^2$ 3  $\left( \begin{array}{c} \\ \end{array} \right)$ VGS 1, ID 1 (Square law device), gm 1. <u>(</u>)  $\therefore g_m(BJT) > g_m(MOS)$ (jj)  $\left( \begin{array}{c} \\ \\ \end{array} \right)$ Gain (BJT) > Gain (MOS \* Collector is Lightly doped (B) Base is moderally doped

-> When Packing density and power consumption is nearn concern then we prefer CMOS ICIA.